搜索结果: 1-15 共查到“电子技术 circuits”相关记录63条 . 查询时间(0.125 秒)

西安电子科技大学电子工程学院模拟电子线路英文课件Chapter11 Feedback Circuits

西安电子科技大学电子工程学院 模拟电子线路 英文课件 Chapter11 Feedback Circuits

2020/6/10

西安电子科技大学电子工程学院模拟电子线路英文课件Chapter11 Feedback Circuits。

东南大学单伟伟、杨军团队在2019 Symposia VLSI Technology and Circuits国际会议发表高能效AES电路成果(图)

东南大学 单伟伟 杨军 2019 高能效 AES电路

2019/8/8

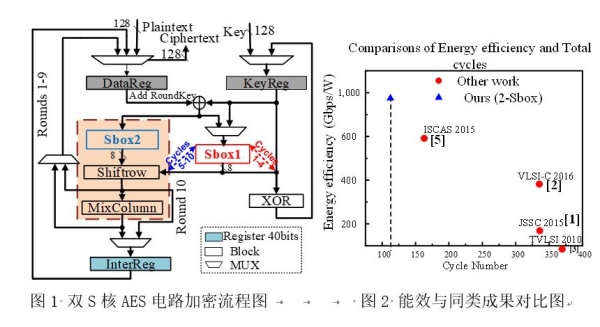

2019年6月9至14日,电子科学与工程学院单伟伟教授、杨军教授等赴日本参加Symposia VLSI Technology and Circuits会议。单伟伟教授在Symposium on VLSI Circuits分会的C20 session作报告,主题为“A 923Gbps/W, 113-Cycle, 2-Sbox Energy-efficient AES Accelerator in 2...

电子科技大学本科生在IEEE Transactions on Circuits and Systems I上发表论文(图)

电子科技大学 本科生 IEEE Transactions on Circuits and Systems I IEEE电路与系统

2019/5/21

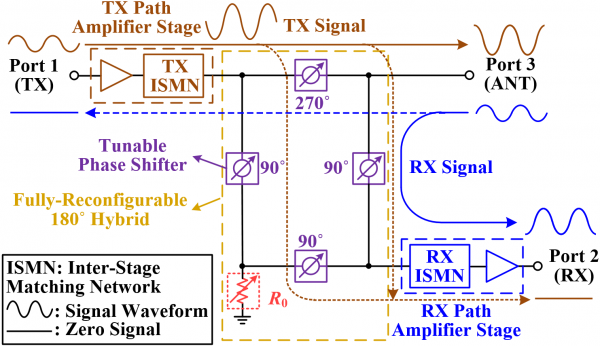

近日,我校电子薄膜与集成器件国家重点实验室、集成电路特色研究中心、电子学院罗讯教授团队大四本科生邓至贤,在IEEE Transactions on Circuits and Systems I(IEEE TCAS-I)发表题为“Tunable quasi-circulator based on a compact fully-reconfigurable 180° hybrid for full-...

Field-programmable Integrated Circuits-Overview and Future Trends

Field-programmable Integrated Circuits Overview Future Trends

2015/8/14

Field-programmable Integrated Circuits-Overview and Future Trends.

In this paper we discuss the question of when the Volterra series is appropriate for nonlinear circuits. We determine that the Volterra series representation is appropriate for circuits with fading me...

Uniqueness of circuits and systems containing one nonlinearity

The nonlinear circuits nonlinear nonlinear elements

2015/8/13

We study systems containing one memoryless nonlinearity. We show that two such systems have the same I/O operator only when they are related by simple scaling, delay, and loop transformations. The the...

Optimizing dominant time constant in RC circuits

Resistance capacitance circuit measuring signal circuit convex optimization conductance

2015/8/11

We propose to use the dominant time constant of a resistor-capacitor (RC) circuit as a measure of the signal propagation delay through the circuit. We show that the dominant time constant is a quasico...

Optimization of inductor circuits via geometric programming

Optimization design inductance rf circuit fixed inductance vibration frequency inductance design

2015/8/11

We present an efficient method for optimal design and synthesis of CMOS inductors for use in RF circuits. This method uses the the physical dimensions of the inductor as the design parameters and hand...

Optimization of phase-locked loop circuits via geometric programming

Phase-locked loop circuit geometric programming frequency phase lock loop

2015/8/11

We describe the global optimization of phase-locked loop (PLL) circuits using geometric programming (GP). Equations for the jitter, frequency range, and power of the PLL are presented in GP form. An a...

ORACLE: Optimization with recourse of analog circuits including layout extraction

Optimization with recourse

2015/8/11

Long design cycles due to the inability to predict silicon realities is a well-known problem that plagues analogRF integrated circuit product development. As this problem worsens for technologies belo...

A new method for design of robust digital circuits

Logic process optimizing circuit digital circuit parameters function monte carlo

2015/8/11

As technology continues to scale beyond 100nm, there is a significant increase in performance uncertainty of CMOS logic due to process and environmental variations. Traditional circuit optimization me...

Functional Verification of Arithmetic Circuits using Linear Algebra Methods

Functional Verification Arithmetic Circuits Linear Algebra SMT Arithmetic bit-level Equivalence checking

2014/12/8

This thesis describes an efficient method for speeding up functional verification of arithmetic circuits namely linear network such as wallace trees, counters using linear algebra techniques. The circ...

Multi-Valued Majority Logic Circuits Using Spin Waves

Spin Wave Multi-valued logic Majority logic

2014/12/8

With increasing data sets for processing, there is a requirement to build faster and smaller arithmetic circuits. One of the ways to improve the performance of higher order arithmetic units is to redu...

Effect of Clock and Power Gating on Power Distribution Network Noise in 2D and 3D Integrated Circuits

Supply Noise Power Gating Clock Gating Wavelet Analysis Linear Programming Genetic Algorithm

2014/12/8

In this work, power supply noise contribution, at a particular node on the power grid, from clock/power gated blocks is maximized at particular time and the synthetic gating patterns of the blocks tha...

Researchers have made great progress in recent years in the design and creation of biological circuits ― systems that, like electronic circuits, can take a number of different inputs and deliver a par...